- 您现在的位置:买卖IC网 > Sheet目录1221 > IPR-ED8B10B (Altera)IP 8B10B ENCODER/DECODER RENEW

�� �

�

�

�8b10b� Encoder/Decoder� MegaCore� Function� (ED8B10B)� Data� Sheet�

�I/O� Signals�

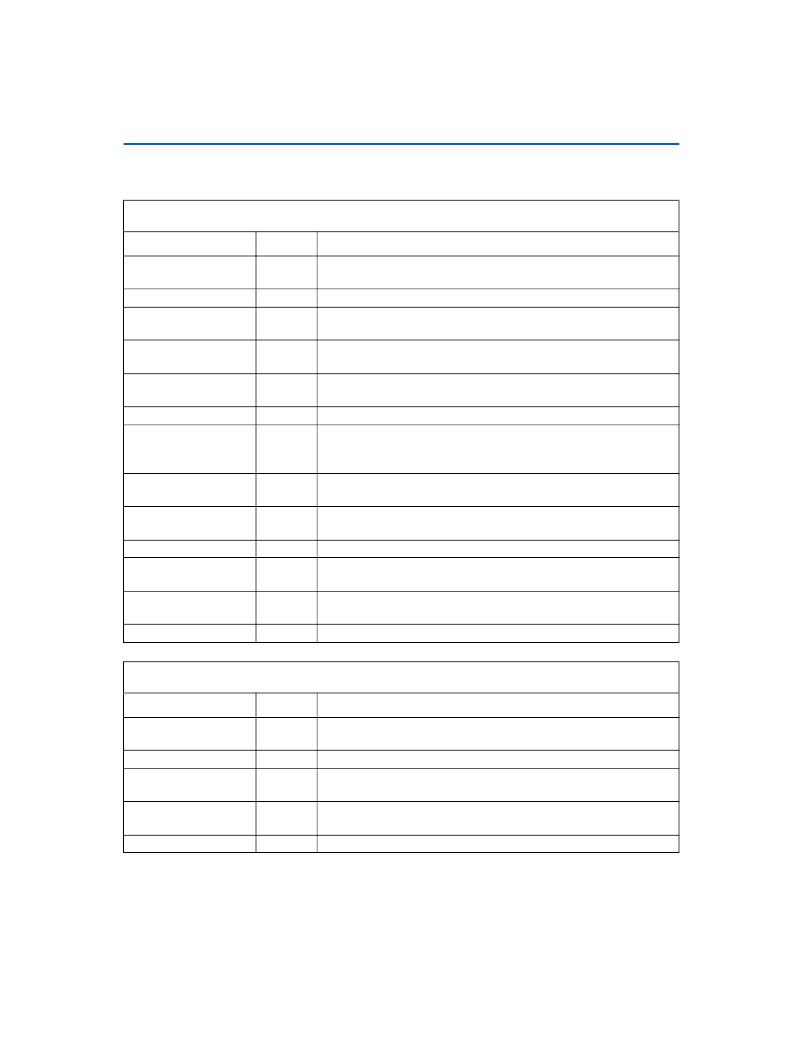

��Table� 2.� Encoder� I/O� Signals�

�Signal� Name�

�clk�

�reset_n�

�kin�

�enable�

�idle_ins�

�datain[7:0]�

�rdin�

�rdforce�

�kerr�

�dataout[9:0]�

�valid�

�rdout�

�rdcascade�

�Direction�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Output�

�Output�

�Output�

�Output�

�Output�

�Description�

�Clock.� The� input� is� latched,� and� the� result� is� output� on� this� clock.� There�

�is� a� three� clock� cycle� latency� between� the� input� and� output.�

�Active� low,� reset.� Asynchronously� resets� all� registers� in� the� core.�

�Command� byte� indicator.� When� high,� indicates� that� the� input� is� a�

�command� byte,� not� a� data� byte.�

�Enable� encoder� signal.� When� high,� indicates� that� the� data� currently�

�present� on� the� datain� input� is� to� be� encoded.�

�Idle� character� insert.� When� high,� idle� (K28.5)� characters� are� inserted�

�when� enable� is� not� asserted.�

�Data� input.� This� is� the� 8-bit� input� word,� data� or� command.�

�Running� disparity� input.� When� rdforce� is� high,� the� value� on� this� pin� is�

�used� as� the� current� running� disparity� instead� of� the� internally� generated�

�one.�

�Force� running� disparity.� When� high,� the� rdin� value� overrides� the�

�internally� generated� running� disparity.�

�Special� K� character� error.� This� signal� is� set� high� when� enable� and� kin�

�are� high� and� the� value� on� datain� is� not� a� valid� special� K� character.�

�Data� output.� This� is� the� 10-bit� encoded� output.�

�Valid� signal.� When� high,� indicates� that� a� valid� encoded� word� is� present�

�on� the� dataout� output.�

�Running� disparity� output.� The� current� running� disparity� (after� encoding�

�the� word� present� on� the� dataout� output).�

�Cascaded� Running� disparity.� Used� when� encoders� are� cascaded.�

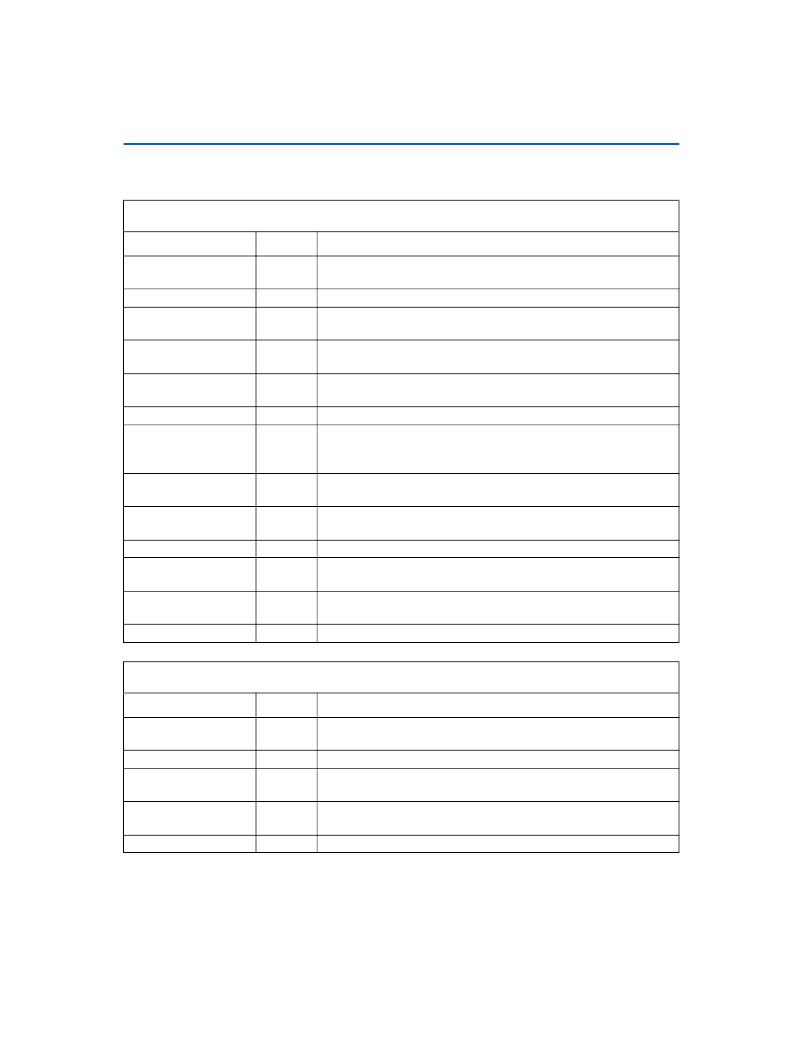

�Table� 3.� Decoder� I/O� Signals�

�Signal� Name�

�clk�

�reset_n�

�idle_del�

�enable�

�datain[9:0]�

�Altera� Corporation�

�Direction�

�Input�

�Input�

�Input�

�Input�

�Input�

�Description�

�Clock.� The� input� is� latched,� and� the� result� output� on� this� clock.� There� is�

�a� three� clock� cycle� latency� between� the� input� and� output.�

�Active� low,� reset.� Asynchronously� resets� all� registers� in� the� core.�

�Idle� delete� signal.� When� high,� idle� words� (K28.5)� are� removed� from� the�

�stream� (i.e.� valid� is� set� low� when� idle� words� are� received).�

�Enable� decoder� signal.� When� high,� indicates� that� the� data� currently�

�present� on� the� datain� input� is� to� be� decoded.�

�Data� input.� This� is� the� 10-bit� encoded� input� word.�

�9�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IPS-VIDEO

IP VIDEO/IMAGE PROCESSING SUITE

IRAC1150-300W

DEMO BOARD FOR IR1150S

IRAC1150-D2

BOARD CONTROL FOR IR1150S

IRAC5001-HS100A

KIT EVAL ORING DEMO BOARD/IR5001

IRADK10

KIT DESIGN 3-PH 115-230ACV MOTOR

IRADK31

DESIGN KIT 1/4 HP DC FOR IR31XX

IRAUDAMP1

KIT REFERENCE DESIGN W/IR2011S

IRAUDAMP4

KIT 2CH 120W HALF BRDG AUDIO AMP

相关代理商/技术参数

IPR-FFT

功能描述:开发软件 FFT/IFFT MegaCore RENEWAL

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPR-FIR

功能描述:开发软件 FIR Compiler MegaCore RENEWAL

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPR-FIRII

功能描述:开发软件 FIR Compiler II MegaCore RENEWAL

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPRI2CCMFP001

制造商:System Level Solutions (SLS) 功能描述:IP CORE, FPGA, I2C CNTLR, FOR CYCLONE, STRATIX, Software Application:IP CORE, In

IPR-ILKN/100G

功能描述:开发软件 Interlaken - 100G MegaCore RENEWAL

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPR-ILKN/50G

功能描述:开发软件 Interlaken - 50G MegaCore RENEWAL

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPR-INTLKN/100G12L

功能描述:开发软件 Interlaken - 100G MegaCore RENEWAL

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPR-INTLKN/100G20L

功能描述:开发软件 Interlaken - 100Gb MegaCore RENEWAL

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors